Semiconductors are not “made” in the abstract. They are assembled through one of the most exacting industrial processes on earth: a sequence of transformations that starts with sand-derived silicon and ends with a chip small enough to sit on a fingernail yet powerful enough to run data centers, smartphones, cars, factory robots, and AI systems.

What makes semiconductor manufacturing so consequential is not just the number of steps. It is the fact that each step depends on the one before it, and almost every step can introduce defects that reduce performance, lower yields, or scrap an entire wafer. The result is a supply chain that is both elegant and brittle. It is a feat of materials science, precision engineering, clean-room discipline, and global logistics—one that powers the modern technology stack while remaining vulnerable to contamination, tooling bottlenecks, and geopolitical shocks.

1. Start with silicon, but not the way people imagine

The process begins with silicon, usually extracted from quartz and refined into extremely pure polysilicon. This is not the gritty material people associate with sand; it is purified to an extraordinary degree because even tiny amounts of contamination can alter electrical behavior later on.

That purified silicon is melted and grown into a single crystal ingot, typically using the Czochralski process. A seed crystal is dipped into molten silicon and slowly pulled upward while rotating, forming a large cylindrical crystal with a uniform atomic structure. This matters because chips rely on predictable electrical properties across the entire wafer. Crystal defects at this stage can haunt the rest of the process.

The ingot is then sliced into thin wafers, polished until they are nearly mirror-perfect, and cleaned. At this point, the wafer is not yet a chip. It is the blank substrate on which thousands of identical circuits will be built.

2. Build the transistor stack layer by layer

Modern chips are not carved from one block of material. They are constructed in layers, each one defined with nanometer-scale precision. The core building block is the transistor, which acts like a switch controlling the flow of electricity.

To form those structures, fabs repeat a small set of processes many times: deposition, lithography, etching, doping, and planarization. This repeated layering is what gives semiconductor manufacturing its complexity. A leading-edge chip may require hundreds of process steps before it is complete.

3. Deposit thin films onto the wafer

Deposition is how fabs add material to the wafer surface. These films can be conductive, insulating, or semiconducting, depending on the layer’s purpose. Methods include chemical vapor deposition, physical vapor deposition, and atomic layer deposition, each suited to different materials and thickness requirements.

These films are not decorative. They form gates, contacts, interconnect barriers, dielectric layers, and other structures that define how electrons move through the chip. At advanced nodes, some layers are just a few atoms thick. That level of control is one reason semiconductor tools are so expensive and so difficult to operate.

4. Use lithography to print the circuit pattern

Lithography is the step that gets the most public attention, and for good reason. It is the process of projecting a circuit pattern onto the wafer using light-sensitive material called photoresist.

First, the wafer is coated with photoresist. Then a lithography system—often using deep ultraviolet light, and at the most advanced nodes, extreme ultraviolet or EUV—exposes selected areas through a mask. The exposed resist changes chemically, allowing the pattern to be developed and transferred to the underlying layer.

This is where much of the industry’s bottleneck lives. The wavelength of light, the precision of the optics, the quality of the masks, and the stability of the environment all determine how finely a chip can be patterned. EUV machines are among the most complex industrial systems ever built, and their scarcity has made them strategic assets in the semiconductor supply chain.

5. Etch away what should not remain

Once the pattern is printed, the unwanted material must be removed. That is the job of etching. In dry etching, plasma removes material selectively from exposed regions. In wet etching, chemical solutions dissolve target layers.

Etching is one of the most delicate balancing acts in chipmaking. It must remove the right amount of material without damaging neighboring structures. At advanced nodes, the difference between success and failure can be measured in a handful of atoms. If the etch is too aggressive, the transistor geometry changes. If it is too weak, the circuit does not form correctly. Either way, yield suffers.

6. Dope the silicon to create electrical regions

Pure silicon does not behave like a useful transistor on its own. To control conductivity, fabs introduce tiny amounts of other elements in a process called doping. Common dopants include boron, phosphorus, and arsenic.

Doping creates regions with different electrical characteristics, allowing engineers to build the source, drain, and channel structures that make transistors switch. The exact placement and concentration of these impurities is critical. Too much or too little doping can change threshold voltage, leakage current, and switching speed.

In other words, chips are not just shaped; they are electrically tuned.

7. Flatten the wafer and repeat the cycle

After deposition, lithography, etching, and doping, the surface is rarely perfectly flat. But the next layer depends on a smooth foundation. That is where chemical mechanical polishing, or CMP, comes in. It combines chemical slurry and mechanical abrasion to remove excess material and flatten the wafer.

CMP is one of the least glamorous steps in the fab, but without it, modern multilayer chips would be impossible to build reliably. Each cycle prepares the wafer for the next patterning round. The process repeats again and again until the transistor layer and the interconnect stack are complete.

This repetition is the hidden logic of semiconductor manufacturing: build, pattern, remove, flatten, verify, repeat. The chip is not made in one dramatic moment. It emerges through disciplined iteration.

8. Connect the transistors into a functioning circuit

Once the transistors are formed, the fab begins wiring them together with multiple metal layers. These interconnects route power and signals across the chip. In a modern processor, the wiring stack is just as important as the transistors themselves, because performance is increasingly limited by how efficiently data can move.

As chips have scaled, interconnect delay, resistance, and capacitance have become major design constraints. This is one reason advanced packaging and chiplet architectures matter so much: the industry is trying to reduce the distance data has to travel while maintaining performance gains.

9. Test the wafer before it is cut apart

Before a wafer is diced into individual dies, it is tested electrically. This wafer probe stage identifies functional chips and catches defects early. Not every die on a wafer will pass, even in a highly optimized fab. Yield—the percentage of usable chips—is one of the most important economic variables in semiconductor manufacturing.

A tiny defect can ruin a die, and a small percentage change in yield can dramatically alter cost per chip. This is why leading-edge manufacturing is so capital-intensive: companies are not just buying tools, they are buying process control, statistical consistency, and lower defect rates.

10. Dice, package, and test again

After wafer-level testing, the wafer is cut into individual dies. Those dies are then packaged, which protects the silicon and connects it to the outside world. Packaging is no longer a back-end afterthought. In many markets, it is a performance differentiator.

Traditional packaging places one die in a protective housing. Advanced packaging may stack chips vertically, connect multiple dies into a single module, or integrate memory and logic more tightly. This matters for GPUs, AI accelerators, networking chips, and mobile processors, where power delivery and bandwidth are central to performance.

Once packaged, the chips are tested again to verify functionality, thermals, and reliability. Only after passing these checks do they ship into the broader electronics supply chain.

Where the system breaks down

Semiconductor manufacturing is a triumph of control, but it fails in predictable places. Contamination is one. A microscopic particle can ruin a patterned layer. Tool downtime is another. The fab depends on a synchronized fleet of highly specialized machines, and if one critical tool stalls, the workflow can back up quickly. Yield loss is perhaps the most expensive failure mode, because defects multiply the cost of every usable chip that does emerge.

There are also structural bottlenecks outside the fab itself. EUV lithography tools are scarce and expensive. Advanced packaging capacity is constrained. High-purity materials and specialty chemicals depend on a global supplier base. Even electricity, water, and ultrapure chemical handling are not simple inputs; they are infrastructure requirements.

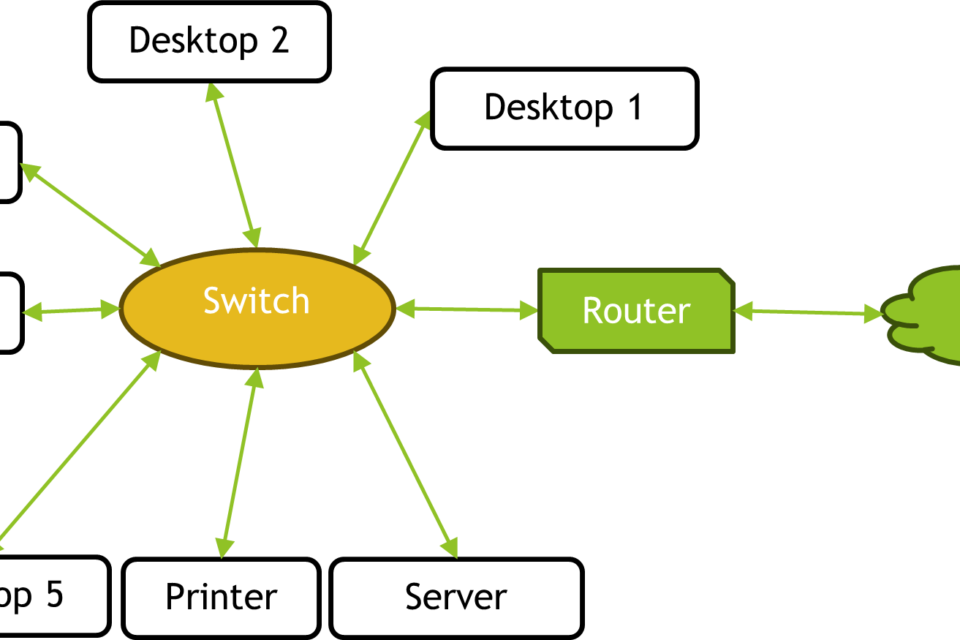

That is why semiconductor manufacturing is best understood as an industrial stack, not just a factory. The fab sits at the center, but it depends on a web of upstream materials, precision tools, process software, packaging providers, and downstream system designers.

Why this matters beyond the chip industry

Chips are the substrate of modern compute. Every data center, robot, industrial controller, power inverter, and AI accelerator depends on them. But the semiconductor industry is also a lesson in how modern infrastructure works: it is distributed, specialized, expensive, and only as strong as its weakest link.

Understanding how semiconductors are made step by step makes one thing clear. The chip is not just a product. It is the endpoint of an enormous industrial choreography, where precision and fragility coexist. That is what makes the sector so strategically important—and why seemingly minor disruptions in a fab can ripple through the entire technology economy.

Image: Chip RIFC heart.jpg | Own work | License: CC BY-SA 4.0 | Source: Wikimedia | https://commons.wikimedia.org/wiki/File:Chip_RIFC_heart.jpg